Architettura del microprocessore Intel 8086 per Informatica

Slide di Università sull'architettura 8086 del microprocessore Intel. La presentazione, un Pdf di Informatica, descrive le caratteristiche principali del microprocessore Intel 8086, approfondendo le funzioni della Bus Interface Unit (BIU) e della Execute Unit (EU) attraverso diagrammi a blocchi.

Mostra di più18 pagine

Visualizza gratis il Pdf completo

Registrati per accedere all’intero documento e trasformarlo con l’AI.

Anteprima

Architettura 8086

D8086 L3093607 |INTEL@1978 Architettura 8086 Parte 1x86 - Famiglia di Architetture CISC

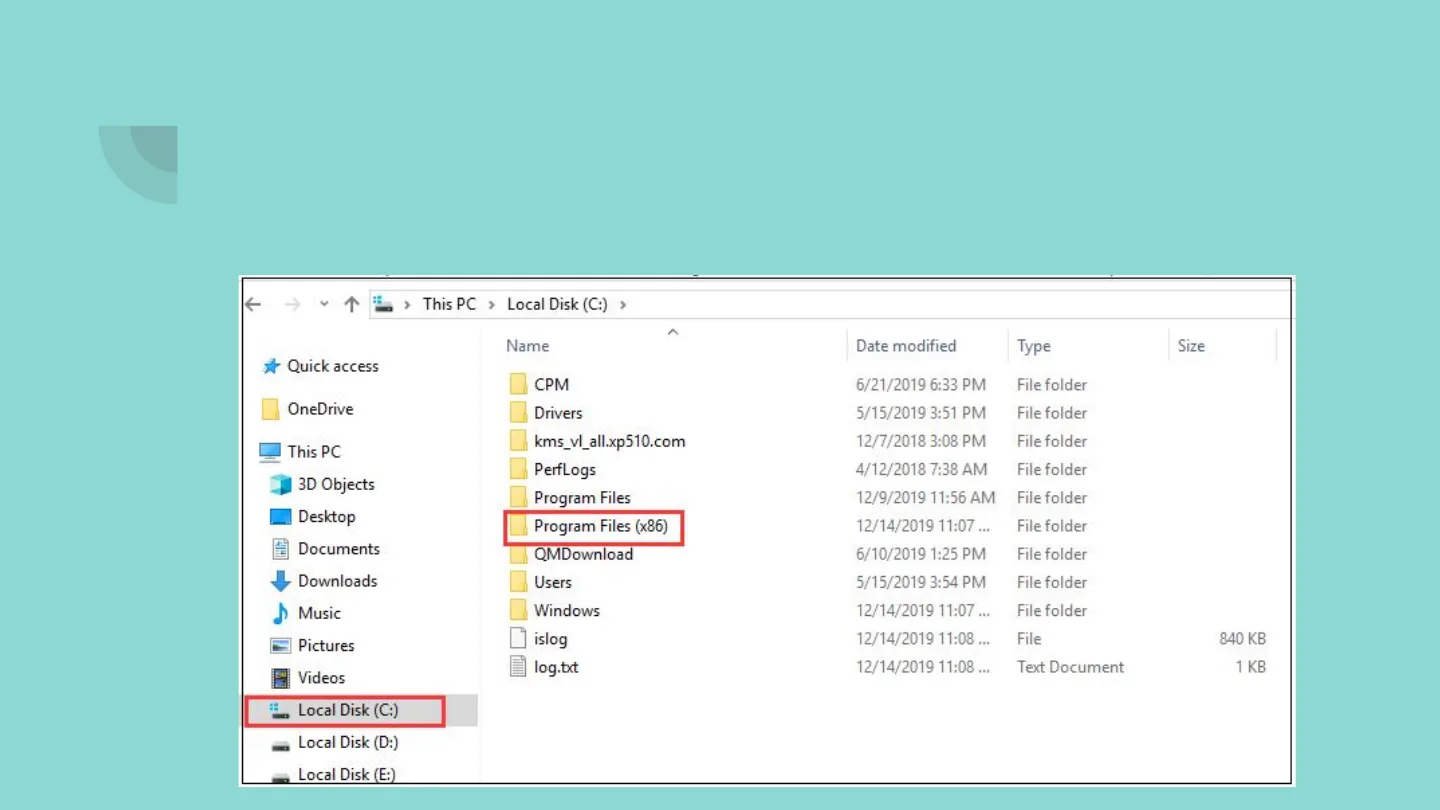

> This PC > Local Disk (C:) >

File System

Name Date modified Type Size Quick access CPM 6/21/2019 6:33 PM File folder OneDrive Drivers 5/15/2019 3:51 PM File folder kms_vl_all.xp510.com 12/7/2018 3:08 PM File folder This PC PerfLogs 4/12/2018 7:38 AM File folder 3D Objects Program Files 12/9/2019 11:56 AM File folder Desktop Program Files (x86) 12/14/2019 11:07 ... File folder Documents QMDownload 6/10/2019 1:25 PM File folder Downloads Users 5/15/2019 3:54 PM File folder Music Windows 12/14/2019 11:07 File folder Pictures islog 12/14/2019 11:08 File 840 KB log.txt 12/14/2019 11:08 Text Document 1 KB Videos Local Disk (C:) Local Disk (D:) Local Disk (E:)x86

Famiglia di Architetture x86

- x86 è una famiglia di architetture CISC inizialmente sviluppate da Intel basate sul microprocessore Intel 8086.

- L'8086 è stato introdotto nel 1978 come estensione completamente a 16 bit del microprocessore 8080 a 8 bit di Intel

- Il termine "x86" è nato perché i nomi di diversi successori del processore Intel 8086 terminano con "86", inclusi i processori 80186, 80286, 80386 e 80486.

- A partire da giugno 2022, la maggior parte dei computer desktop e laptop venduti si basa sulla famiglia di architetture x86, mentre le categorie mobili come smartphone o tablet sono dominate dall'architettura ARM.

- Nella fascia alta, x86 continua a dominare i segmenti di workstation e cloud computing ad alta intensità di calcolo.Obiettivo

Architettura 8086

- Architettura 8086

- Ciclo Fetch-Decode-Execute 8086

- Programmazione Assembly 8086

Diagramma a Blocchi

Adder Upper regs Decode Lower regs ALU Microcode

Funzione memcpy

; _ memcpy(dst, src, len) ; Copy a block of memory from one location to another. : ; Entry stack parameters [BP+6] = len, Number of bytes to copy [BP+4] = src, Address of source data block [BP+2] = dst, Address of target data block ; Return registers AX = Zero 0000:1000 org 1000h ; Start at 0000:1000h 0000:1000 memcpy proc 0000:1000 55 push bp ; Set up the call frame 0000:1001 89 E5 mov bp, sp 0000:1003 06 push es ; Save ES 0000:1004 8B 4E 06 mov cx, [bp+6] ; Set CX = len 0000:1007 E3 11 jcxz done ; If len = 0, return 0000:1009 8B 76 04 mov si, [bp+4] ; Set SI = src 0000:100C 8B 7E 02 mov di, [bp+2] ; Set DI = dst 0000:100F 1E push ds ; Set ES = DS 0000:1010 07 pop es 0000:1011 8A 04 loop mov al, [si] ; Load AL from [src] 0000:1013 88 05 mov [di], al ; Store AL to [dst ] 0000:1015 46 inc si ; Increment src 0000:1016 47 inc di ; Increment dst 0000: 1017 49 dec Cx ; Decrement len 0000:1018 75 F7 jnz loop ; Repeat the loop 0000:101A 07 done pop es ; Restore ES 0000:101B 5D pop bp ; Restore previous call frame 0000: 101C 29 CO sub ax, ax ; Set AX = 0 0000: 101E C3 ret ; Return 0000: 101F end proc

Control CPU Intel 8086

- Set di istruzioni: x86-16

- 29.000 Transistor

- Clock 5-10 Mhz

- 40 pin D8086 L3093607 |INTEL@1978

Architettura 8086 - Visione sommaria

- La Bus Interface Unit (BIU) ha 3 compiti:

- Fetch

- Calcolo indirizzo fisico

- Gestione coda di pre-fetch da 6byte

- La Execute Unit (EU) ha 2 compiti:

- Decode

- Execute

Architettura 8086 - Visione in profondità

To memory and Input/ Output BIU 6 Σ 5 4 PA = Seg X 10H 3 + offset 2 CS SS DS ES IP Control Unit EU AH AL -AX General BH BL -BX Purpose CH CL -CX DH DL -DX SP BP Operands SI DI Flags Block Diagram of 8086 Microprocessor Electronics Desk ALU Registers 6-Byte pre-fetch queue

Rappresentazione Esadecimale

https://antonioquermani.jimdofree.com/matematica/sistemi-di-numerazione/sistema-esadeci male/ DECIMAL HEX BINARY 0 0 0000 1 1 0001 2 2 0010 3 3 0011 4 4 0100 5 5 0101 6 6 0110 7 7 0111 8 8 1000 9 9 1001 10 A 1010 11 B 1011 12 C 1100 13 D 1101 14 E 1110 15 F 1111

Registri General-Purpose e Puntatore

" emulator: es1_n4.exe_ file debug view virtual devices virtual drive help LOAD reload 11 step back single step run st registers H L AX BX CX 31 1F 07203: 8E 142 A 07204: DA 218 07205: B8 184 @ CS 0720 IP 07208: 8E 142 A SS 0716 07209: D8 216 Ï SF 0100 0720A: B9 185 # BF 0720B: FE 254 0720C: 20 032 SPA SI 0720D: BB 187 1 DI 0720E: 01 001 0 DS 5755 07210: 89 137 ë ES 07211: ØF 015 ¢ T screen source reset aux vars debug

- Registri General-Purpose

- Sono posizionati dentro la EU.

- Sono 4 (AX, BX, CX, DX).

- Hanno dimensione 16bit.

- Il programmatore può scrivere/leggere un dato sul registro general-purpose (no istruzione).

- Posso utilizzarli come un unico registro da 16bit. oppure come due sotto-registri da 8bit.

- Registri Puntatore

- Sono 4 (SP, BP, SI, DI).

- Hanno dimensione 16bit. 5720:0000 07200: BA 186 07201: 20 032 SPA 07202: 07 007 BEEP DX 07206: 00 000 NULL 07207: 07 007 BEEP 0720F: 00 000 NULL

Memoria

Random Access Memory

0720:0000 upda 0720:0000: BA 0720:0001: 20 0720:0002: 07 0720:0003: 8E 0720:0004: DA Nella cella 0720:0001 c'è il dato 20h (in decimale 32, in binario 00100000)

- La CPU 8086 è dotata di

- Celle di memoria a 8bit (2 cifre esadecimali)

- Bus Dati a 16bit

- Bus Indirizzi a 20bit

- Posso referenziare massimo 220 celle di memoria

- Dimensione memoria totale: 22º celle di memoria * 8bit = 1Mbyte

Memoria - Dati e Istruzioni

- La CPU 8086 riprende il modello di Von Neumann quindi nella memoria avrò:

- dati + istruzioni registers 0720:000A 0720:000A H L AX 07 07200: BA 186 MOV DX, 00720h 07201: 20 032 SPA MOV DS, DX 07202: 07 007 BEEP MOV AX, 00700h CX 01 1F MOV DS, AX DX 07 25 07205: B8 184 MOV BX, 00001h CS 0720 07206: 00 000 NULL MOV [BX], CX IP 000A 07207: 07 007 BEEP MOV BX, 00001h SS 0710 07209: D8 216 MOV AL, [BX] MOV AH, 00h INT 016h SP 0720A : B9 185 T 0720B: FE 254 MOV AH, 04Ch BP 0720C: 20 032 SPA INT 021h SI 0720D: BB 187 NOP DI 0720E: 01 001 NOP DS 0700 07210: 89 137 ë NOP ES 0700 07211: OF 015 ¢ . . BX 07203: 8E 142 Ä 07204: DA 218 MOV CX, 020FEh 07208: 8E 142 Ä L'istruzione MOV CX, 020FEh è contenuta nella memoria nelle celle 0720Ah, 0720Bh, 0720Ch 0720F: 00 000 NULL NOP

Celle di memoria - Dato

- Se il dato è di 8bit (1byte) => 1 Cella di memoria

- Se il dato è di 16bit (2byte) => 2 Cella di memoria Random Access Memory 0720:0000 upda 0720:0000: BA 0720:0001: 20 0720:0002: 07 0720:0003: 8E 0720:0004: DA Il dato DA8Eh viene disposto in due celle:

- il primo byte nella cella 0720:0004

- il secondo byte nella cella 0720:0003

Gestione della memoria: Little-Endian

- Intel, Digital (poi HP) usano il formato little-endian

- Motorola, IBM usano il formato big-endian 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 . model small . data INIZIO DATA SEGMENT empty DB 10h dup (00h ) FINE DATA SEGMENT . code INIZIO CODE SEGMENT main proc MOV AX, @data MOV DS, AX MOV [0007h], ØAABBh 07105: 07106: 07107: 07108: 07109: 7 0710A: 00 000 000 BB AA 187 170 000 0 000

Celle di memoria - Istruzioni

- Le istruzioni hanno dimensione variabile da 1 a massimo 6 byte. registers H L AX 07 07200: BA 186 A MOV DX, 00720h 07201: 20 032 SPA BX 07202: 07 007 BEEP 07203: 8E 142 A MOV DS, AX 07 20 07205: B8 184 @ MOV BX, 00001h 0726 07206: 00 000 NULL 07207: 07 007 BEEP 000A 07208: 8E 142 Ä 0710 07209: D8 216 Ï SP 0166 0720A : B9 BP 0720C: 20 032 SPA SI 0720D: BB 18/ 1 0720E: 01 001 ( DI 0720F : 00 000 NULL NOP 07210: 89 137 ë NOP 07211: ØF 015 ¢ L'istruzione MOV CX, 020FEh occupa 3 byte, quindi 3 celle di memoria:

- la cella 0720Ah

- la cella 0720Bh

- la cella 0720Ch DS 0700 ES 0706 0720:000A 0720:000A MOV DS, DX MOV AX, 00700h 8 8868 CX DX CS IP 1F 07204: DA 218 r MOV CX, 020FEh MOV [BX], CX MOV BX, 00001h MOV AL, [BX] MOV AH, 00h INT 016h 185 1 0720B: FE 254 MOV AH, 04Ch INT 021h NOP NOP

Memoria - Segmentazione

(CS) (Code Segment) (DS) (Data Segment) (SS) (Stack Segment) (ES) (Extra Segment) Figure: Memory Segmentation (Code, Data, Stack and Extra Segments)

- La memoria è divisa in segmenti

- Dimensione massima di un segmento: 64KByte

- La memoria utilizzata da un programma è divisa in

segmenti che contengono ciascuno un tipo di

informazione:

- o dati

- o istruzioni

- L'8086 prevede 4 tipi di segmenti:

- Code Segment

- Data Segment

- Stack Segment

- Extra Segment

Memoria - Segmenti e Registri

- Per ognuno di questi segmenti esiste:

- Un registro che contiene l'indirizzo base del segmento (l'indirizzo dell'inizio del segmento).

- Un registro che contiene l'offset relativo a quel particolare segmento. registers H AX 07 BX CX 01 1F DX 07 20 CS 0720 IP 000A SS 0710 SP BP SI DI DS 0700 ES 0700

- Code Segment:

- CS: è il registro che contiene l'indirizzo base del Code Segment.

- IP: è il registro che contiene l'offset relativo al Code Segment.

- Warning: Non confondere il registro CS, con il segmento Code Segment

- Nel registro CS c'è solo l'indirizzo base del Code Segment, mentre il vero Code Segment sta nella memoria e contiene le istruzioni del programma.

- Data Segment:

- DS: è il registro che contiene l'indirizzo base del Data Segment.

- Warning: Non confondere il registro DS, con il Data Segment

- Nel registro DS c'è solo l'indirizzo base del Data Segment, mentre il vero Data Segment sta nella memoria e contiene i dati del programma.

Memoria - Indirizzo Virtuale

- In 8086 un indirizzo di memoria è costruito:

- Indirizzo Virtuale = Indirizzo Base : Offset

- Dove

- Indirizzo base: è l'indirizzo che indica l'inizio del segmento

- Offset: è la distanza dall'inizio del segmento (dall'indirizzo base) registers 0720:000A 0720:000A H L AX 07 07200: BA 186 | 1 MOV DX, 00720h 07201: 20 032 SPA MOV DS, DX MOV AX, 00700h CX 01 1F 07203: 8E 142 / MOV DS, AX DX 07 20 MOV CX, 020FER CS 0720 07206: 00 000 NULL IP 000A 07208: 8E 142 A SS 0710 SF 0100 0720A: B9 185 0720B : FE 254 : BP 0720C : 20 032 SPA SI 0720D: BB 187 7 NOP DI 5555 0720E: 01 001 NOP DS 0706 07210: 89 137 ë NOP 0720=Indirizzo Base 000A=Offset (dista 10 celle dall'inizio del segmento) Indirizzo Virtuale= 0720:000A MOV [BX] CX MOV BX, 00001h MOV AL, [BX] MOV AH, 00h INT 016h MOV AH, 04Ch INT 021h 0720F: 00 000 NULL NOP ES 700 07211: 0F 015 ¢ BX 07202: 07 007 BEEP 07204: DA 218 r 07205: B8 184 @ MOV BX, 00001h 07207: 07 007 BEEP 07209: D8 216 Ï

Trasformazione da Indirizzo Virtuale a Indirizzo Fisico

- Formula: Indirizzo Fisico = Indirizzo base segmento x 10h + Offset registers 0720:000A 0720:000A AX 07 615 07200: BA 186 | MOV DX, 00720h 07201: 20 032 SPA MOV DS, DX MOV AX, 00700h CX 01 1F MOV DS, AX DX 07 26 CS 0720 07206: 00 000 NULL MOV [BX] CX IP 000A SS 0710 07209: D8 216 Ï SP 0100 0720A : B9 185 1 0720B: FE 254 0720C: 20 032 SPA SI 0720D: BB 187 1 0720E: 01 001 NOP DS 0700 07210: 89 137 ë ES 0700 07211: 0F 015 ¢ MOV AH, 04Ch INT 021h NOP DI 0720F: 00 000 NULL NOP NOP ... 0720=Indirizzo Base 000A=Offset Indirizzo Virtuale= 0720:000A Indirizzo Fisico= 0720 x 10h + 000Ah= 0720Ah MOV BX, 00001h MOV AL, [BX] MOV AH, 00h INT 016h BP DA 218 07205: B8 184 MOV CX, 020FEh 07203: 07204: MOV BX, 00001h 07207: 07 007 BEEP 07208: 8E 142 Ä