Apuntes de arquitectura de computadoras de Itba: decodificación, I/O y memoria

Documento de Itba sobre arquitectura de computadoras: decodificación incompleta, I/O, interrupciones y gestión de memoria. El Pdf, un material de estudio para universitarios de Informática, aborda temas como el PIC, paging, swapping y la memoria caché, con esquemas y diagramas explicativos.

Ver más18 páginas

Visualiza gratis el PDF completo

Regístrate para acceder al documento completo y transformarlo con la IA.

Vista previa

Decodificación Incompleta y Direccionamiento

Decodificación incompleta: Por simplicidad o para minimizar la cantidad de componentes no se hacen llegar todas las líneas del bus de direcciones. Por lo tanto aparecen "imágenes". Nunca tenemos que dejar una patita de bus de address sin utilizar. Si por ejemplo, no conectamos la más significativa, se nos rompe el sistema de los chip select, y se puede "llamar" a dos a la misma vez, lo que se llama imagen.

Sistema de Entrada y Salida (E/S)

E/S Aislada

E/S aislada: Una señal especial del micro indica la ejecución de una operación de entrada y salida. Es lo que vimos de IN y OUT.

Interrupción

Interrupción: Una señal externa interrumpe al micro para requerir un servicio de atención.

Acceso Directo a Memoria (DMA)

Acceso directo a memoria (DMA): La información se transfiere directamente a la memoria, no requiere de intervención del CPU. Algunos periféricos acceden directo a la RAM sin pasar por el procesador. Un ejemplo es un disco rígido. Lo que hace el periférico es activar el chip select de la RAM en algunas "zonas" de memoria predefinidas.

Mapeo en Memoria

Mapeo en memoria: Se le otorga un sector de memoria principal al dispositivo. Es decir, consiste en poner un periférico en el mapa de memoria. Formato Texto: se divide la pantalla en 80x25 filas y columnas para imprimir caracteres. Podemos verlo cuando se prende la computadora y se inicia el booteo de la BIOS.

Interrupciones

Son señales externas que interrumpen al microprocesador para requerir un servicio de atención. Requieren ejecutar lo que se llama rutina de atención de interrupción. Estas rutinas en lugar de volver con RET, vuelve con IRET, que es lo mismo pero recupera de la memoria otro tipo de información. Hay dos tipos:

- Interrupción de Hardware: mediante una patita del procesador, le pasamos una cantidad de volts y se interrumpe. Hay dos patitas, INTR y NMI. La primera se puede no prestarle atención (es decir, se puede enmascararla). Esto sirve por si el procesador está ejecutando un proceso importante que no debe ser interrumpido (operaciones atómicas). En la otra, NMI (interrupción no enmascarable), lo que pongamos va a sí o sí interrumpir.

17Arqui - Resumen ITBA

- Interrupción de Software: usando la instrucción INT. Es muy similar a call, pero la gran diferencia es que call llama a una función que hicimos nosotros, y el INT a una que hizo otra persona (por lo general el SO).

Para las interrupciones, siempre se sigue el mismo formato. El microprocesador detiene la ejecución del programa actual, busca en la IDT la posición de la interrupción que llega y busca el puntero a la rutina de atención correspondiente, para luego ejecutarla.

Interrupciones en Multicore

Interrupciones en Multicore: Cada CPU tiene su PIC y afuera existe el APIC donde se conectan los periféricos y dicho PIC decide a que core le tira las interrupciones.

PIC (Controlador Programable de Interrupciones)

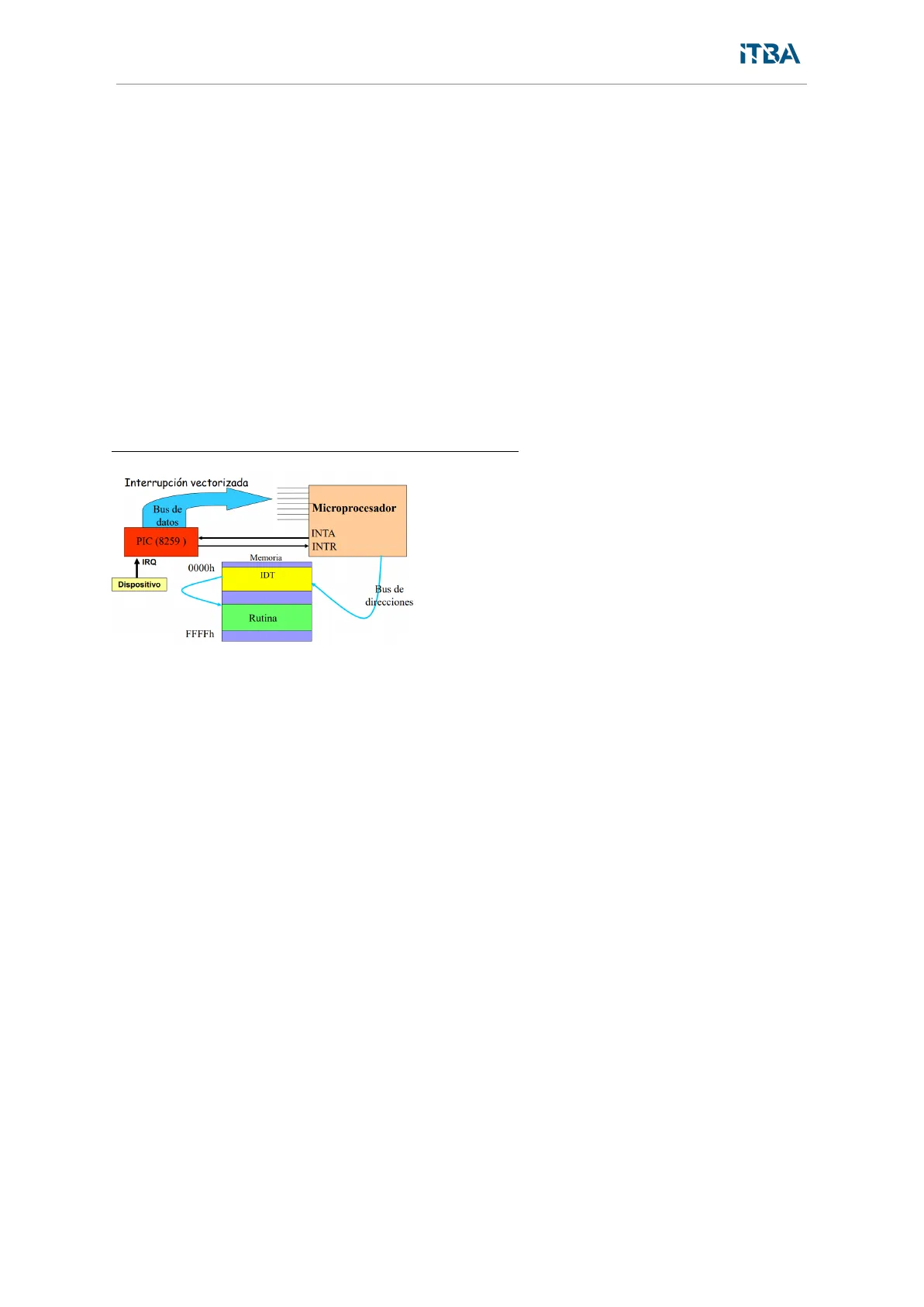

Interrupción vectorizada Vemos que en el microprocesador tiene una sola patita de interrupción para periféricos, se incluyó el PIC (es un periférico) que permite conectar 8 (pues tiene 8 patitas de interrupción) periféricos. Las patitas tienen el nombre de IRQ quiere decir Interrupt Request. El dispositivo interrumpe al PIC, que le "avisa" al procesador y le dice quien es el que quiere interrumpir. Una vez que el procesador sabe qué periférico fue, se fija en la tabla IDT, donde hay punteros a todas las rutinas de interacción de los periféricos (los drivers), la va a buscar y ejecuta la misma. El contenido de la tabla lo programa el que desarrolla el SO. Vemos que la misma está en RAM, por lo que cuando se apaga la compu se borra. Cuando se prende, se recupera del disco cuando se bootea la computadora (al igual que cuando se sube el SO). Esto lo hace la BIOS.

Procedimiento de Interrupción

El procedimiento es el siguiente:

- El dispositivo genera una interrupción a través de una patita IRQ.

- PIC alerta al microprocesador a través de su patita INTR.

- El microprocesador acepta la interrupción a través de su patita INTA.

- Al aceptar la interrupción, a través de BUS DE DATOS el PIC le dice al microprocesador cuál de sus 8 patitas fue la que interrumpió.

- Sabiendo ese dato, el microprocesador va a buscar en la tabla IDT el puntero que corresponde al dispositivo que debe ser atendido.

- Salta a la rutina de atención de interrupción una vez hallado el puntero

18Arqui - Resumen ITBA

Puertos de Entrada y Salida del PIC

Los puertos de entrada y salida en la PC son el 20h y el 21h. El primero se utiliza para programar el PIC y lo utiliza la BIOS al arrancar el sistema. Con la segunda, podemos acceder al registro IMR (Interrupt Mask Register) y setear qué interrupciones llegan al microprocesador y cuáles no.

In al, 21h ; leo mascara del PIC ; 0 = mascara deshabilitada, por lo ; tanto pasa la señal al microprocesador Mov al,0FEh ; por ej. Solo habilito la interrupción de teclado Out 21h, al

EOI (End of Interrupt)

EOI (End of interrupt): Cada rutina de atención de interrupción, luego de correr, debe avisar al PIC que terminó su ejecución. Se puede especificar la IRQ que terminó o enviar un código que indica que finalizó la atención de la última interrupción que llegó. Esa palabra se envía al puerto 20h y el valor que se envía para indicar que finalizó la atención de la interrupción es el valor 20h.

Conexión en Cascada de PICs

Como no alcanzó con un solo PIC para la cantidad de periféricos, se conectó un segundo en cascada. Así, más periféricos pueden interrumpir al procesador. Se utiliza el IRQ2 del Máster para conectar el Slave (el segundo conectado).

Servicio de BIOS

El BIOS al iniciar la PC guarda en memoria rutinas básicas para poder empezar a operar, porque la IDT está vacía en este momento. Estas rutinas básicas están en ROM al igual que la BIOS (que recordemos que al no ser volátil, no se borran cuando se apaga).

Interrupciones de Hardware por Default

| Línea | IRG | INT | Tipo | Descripción |

|---|---|---|---|---|

| IRQO | 08h | Timmer tick (18,2 veces por seg.) | ||

| IRQ1 | 09h | Teclado | ||

| IRQ2 | 0Ah | INT desde 8259A esclavo | ||

| IRQ8 | 70h | Servicio de reloj en tiempo real. | ||

| IRQ9 | 71h | Redireccionamiento por soft. a IRQ2 | ||

| IRQ10 | 72h | Reservada | ||

| IRQ11 | 73h | Reservada | ||

| IRQ12 | 74h | Reservada. | ||

| IRQ13 | 75h | Coprocesador numérico. | ||

| IRQ14 | 76h | Controlador de disco rígido. | ||

| IRQ15 | 77h | Reservada. | ||

| IRQ3 | OBh | COM2 | ||

| IRQ4 | 0Ch | COM1 | ||

| IRQ5 | ODh | LPT2 | ||

| IRQ6 | OEh | FLOPPY | ||

| IRQ7 | OFh | LPTI |

19Arqui - Resumen ITBA Las IRQ son las patitas en los PIC. Vienen por default y se pueden reprogramar o no.

Excepciones

Son exactamente igual que las interrupciones, pero en vez de ser generadas por un periférico o por un programador que pone INT, son generadas por el mismo procesador, que se interrumpe a sí mismo. Dicho formalmente, es un evento generado por el procesador cuando detecta una o más condiciones predefinidas al ejecutar una instrucción. Cuando el procesador detecta un error, se autointerrumpe, va a la IDT y busca cuál de los 32 errores fue el detectado para correr la rutina de interrupción de excepción. Las 32 son:

| Id | Description |

|---|---|

| 0 | Divide error |

| 1 | Debug exceptions |

| 2 | Nonmaskable interrupt |

| 3 | Breakpoint (one-byte INT 3 instruction) |

| 4 | Overflow (INTO instruction) |

| 5 | Bounds check (BOUND instruction) |

| 6 | Invalid opcode |

| 7 | Coprocessor not available |

| 8 | Double fault |

| 9 | (reserved) |

| 10 | Invalid TSS |

| 11 | Segment not present |

| 12 | Stack exception |

| 13 | General protection |

| 14 | Page fault |

| 15 | (reserved) |

| 16 | Coprecessor error |

| 17-31 | (reserved) |

| 32-255 | Available for external interrupts via INTR pin |

La 13 es la conocida como segmentation fault o el pantallazo azul de windows. Es una protección general. El que detecta el error es el procesador, no el SO, porque cuando corre nuestro programa es lo único que corre. Por lo tanto, como no corre el SO, no lo puede detectar. En conclusión, el SO no supervisa nuestras operaciones porque no está corriendo.

Tipos de Excepciones

Existen 3 tipos de excepciones:

- Faults : Excepción que puede corregirse. El procesador guarda en la pila la dirección de la instrucción que produjo la falla.

- Trap : Se utilizan para realizar accesos al sistema operativo.

- Abort: No siempre se puede obtener la instrucción que causó la excepción. Reporta errores severos.

20Arqui - Resumen ITBA

Modo Protegido

Conmutación de Tareas

Recordamos que se ejecuta de un proceso a la vez, con una velocidad tan rápida (orden de los milisegundos) que nosotros creemos que se corre todo a la vez. Cada fracción de tiempo que corre se llama slot time.

El Timer Tick es un integrado en la PC que interrumpe al procesador cada 55ms (por default). Esto lo hace siempre, sin importar si el SO es el único proceso. Es enmascarable, porque está conectado a la IRQ0. Es el que permite la conmutación de tareas, interrumpiendo al PIC como cualquier periférico. La rutina Scheduler de interrupción lo que hace es decidir a quien se le asigna el procesador en cada momento. Se encuentra en el SO, en el kernel space y fue programada por los desarrolladores del SO. Cuando se "corta" un proceso que estaba corriendo, tiene que guardar lo que se llama el contexto de tarea (todos los registros de la misma), para que cuando vuelva a recibir el procesador, siga en el mismo estado. Lo que hace es backupearlo en memoria, y luego cuando vuelve se recupera. Estas tareas, son las que pueden tener errores y mandar el instruction pointer a cualquier lado.

Protección de Tareas

Para evitar que una tarea mande un puntero a otra, el único que puede controlar es, como ya vimos, el procesador, porque el SO no está corriendo. Para que el procesador sepa esto, se le proveen unas "tablas" según desde donde hasta dónde está cada tarea.

Memory Management Unit (MMU)

Intel para dividir la memoria creó dos formas. La unidad de segmentación divide la memoria en partes de tamaño variable, y la unidad de paginación en tamaño fijo. La unidad de paginación se puede apagar pero no la de segmentación. Si tenemos un

21