Multisim: simulazione di circuiti elettronici e Half Bridge

Documento su Multisim per la simulazione di circuiti elettronici. Il Pdf, utile per lo studio universitario di Informatica, descrive le funzionalità del software, la realizzazione di schemi e l'analisi di circuiti come l'Half Bridge, con concetti quali Dead-Time e analisi di Fourier.

Mostra di più15 pagine

Visualizza gratis il Pdf completo

Registrati per accedere all’intero documento e trasformarlo con l’AI.

Anteprima

MULTISIM: Software di simulazione SPICE

MULTISIM Software di simulazione SPICE, ambiente interattivo che permette la visualizzazione in tempo reale del comportamento di circuiti elettronici- analogici, digitali e l'potenza.

Strumenti di Multisim

- DESIGN TOOLBOX -> permette di visualizzare la gerardina della fasi del progetto aperto;

- IN USE LIST -> contiene l'elenco di tutti i componenti in uso nello schema;

- INSTRUMENT TOOLBAR -> tasti per inserire gli strumenti di misura disponibili;

- CIRCUIT WINDOWS -> Spazio che disviluppare lo schema;

- SPREADSHEET VIEW -> permette l'immediata visualizzazione e modifica dei parametri circuitali

REALIZZARE UNO SCHEMATICO IN MULTISIM

Componenti in Multisim

Componenti reali -> componenti presenti fisicamente mei circuiti (resistori, diodi, etc. Vengono rappresentati componenti anche presenti in commer cio, possono essere- stampati proprio con i loro simboli, parametri, .. « (package) così che, quando si passa alla piattaforma Ultiboard, sia possibile visualiz zare il componente come è realmente Componenti virtuali -> Esempio gli strumenti di misura. Questi permettono di definire parametri ma non Non presenti in commercio servono solo per effettuare simulazioni hanno un vero e proprio simbolo, quindi quando si passa a Ultiboard verranno rappresentati tutti con lo stesso disegno La plataforma Ultiboard serve per la creazione dei prototipi di circuiti stampati (PCB).

Integrare Lezione 28/09/23

Quando si usa l'OSCILLOSCOPIO dobbiamo portare il terminale negativo a massa . Quest'ultima deve essere la STESSA di quella usata per il circuito da testare

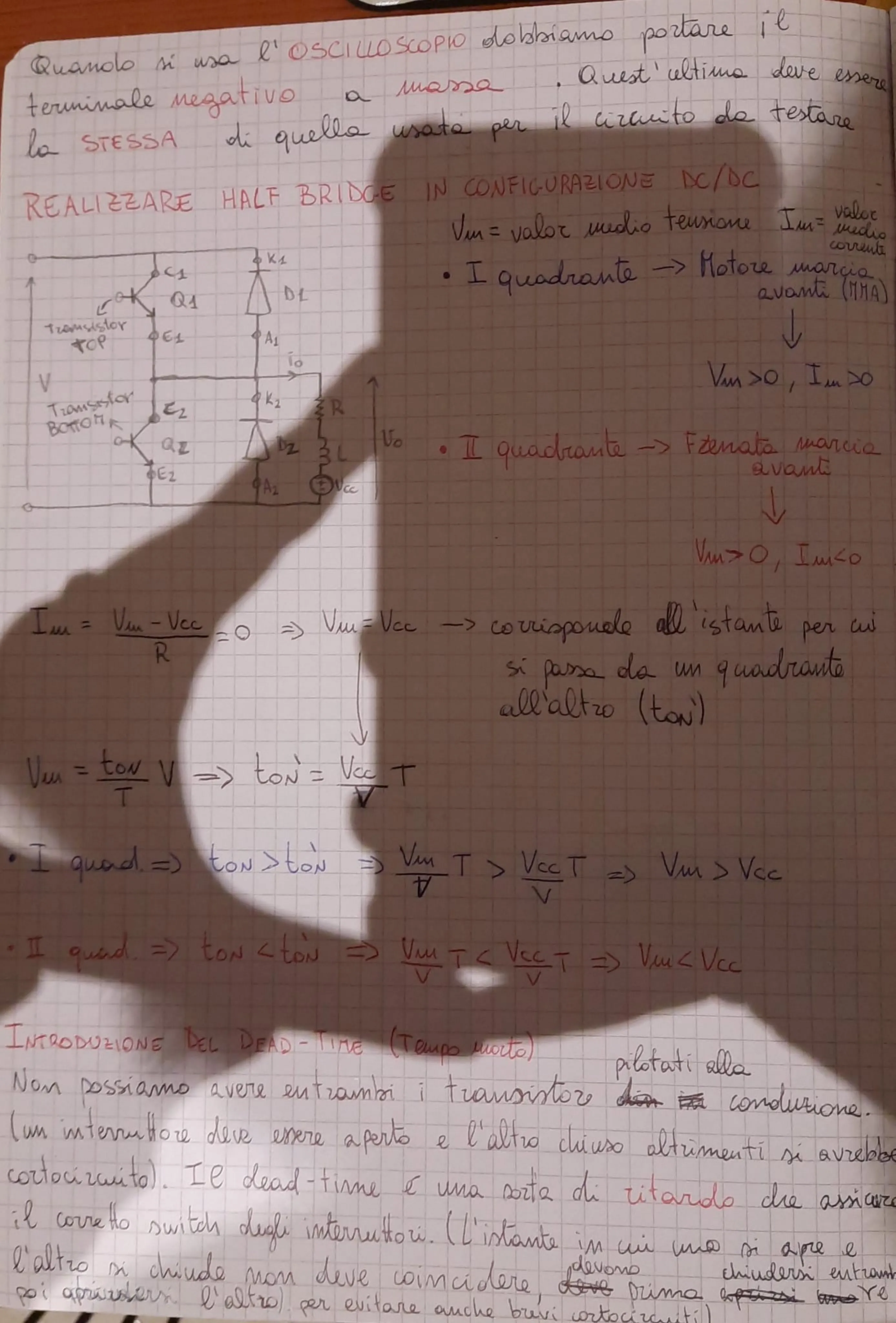

REALIZZARE HALF BRIDGE IN CONFIGURAZIONE DC/DC

valor Um = valor medio tensione Im= medio corrente

- I quadrante -> Motore marcia avanti (MMA)

1 DI OK Q1 Transistor DE1 PAS TOP To V Q K2 ER E2 BL BEZ FAZ G Vm= 0, Imco M = Vm-Vcc R => Vm= Vcc -> corrisponde all'istante per cui si passa da un quadrante all'altro (ton) y Vm = ton V => toN = Vc + T

- I quad .= > ton>ton =>Vm T > VccT => Vm > Vcc A

- II quand => ton < toN => VM T < VCC T => Vu < Vcc

INTRODUZIONE DEL DEAD -TIME (Tempo morto)

pilotati alla Non possiamo avere entrambi i transistore conduzione. (un interruttore deve essere aperto e l'altro chiuso altrimenti si avrebbe cortocircuito). Il dead-time è una sorta di ritardo che assicuro il corretto switch degli interruttori. (L'istante in cui uno si apre e l'altro si chiude non deve coincidere, deve prima ire devono chiudersi entrant poi aprivolersi l'altro) per evitare anche brevi cortocirani

- I quadrante -> Frenata marcia avanti Vo Transistor BOTTOMA Vm >0, Im DO 6 K1Il dead time dipende dalle specifiche di ogni singolo transistor.

Effetti del Dead-time Integrare lecione 06/10/23

Si cerca di ridurre gli effetti riducendo il più possibile il dead time.

- A causa dei tempi morti si creano deformazioni della tension in uscita. Errore -> dovuto al Tsw AVO = + Vale . TD dead-time Vdc = tensione continua di alimentazione con TD = dead-time Tsw = periodo di switching i transistor sono

- Si verificano istanti in cui entrambi sono spenti e la corrente è costretta a circolare nei chiodi. IM DI -> iOLO => Vo - Vale IM D2 -> 10>0 => Vo = - Vdc Durante il tempo morto la tensione sul carico dipende solo dal verso della corrente To che circola nel carico

- In base al segno della corrente si perde o si aggiunge un impulso al segurale di pilotaggio. Es. carico passivo -> correnti effetto tensione si negativo riduce di una quantità (cunico-induttivo) assorbita si perde un - positiva impulso iniziale carico attivo corrente negative Vok = Vok - sign(iv). Avo tensione reale aumenta di una quantità con Voi = tensione desiderato Vok= tensione ottenuta viale Iv = corrente in uscita sign = segno

- Il dead time introduce armoniche a bassa frequenza difficili da filtrare.

Schema circuitale

Come è fatto lo schema circuitale.

- Generatore di Sgnal impulsivo in ingresso

- PONTE RC -> par l'implementazione del DEAD-TINE ( filtro per il segnale)

- COMPARATORE -> per confrontare segnale filtrato e segnali di riferimento. Al gin 5 va collegata un generatore di tensione poiché il dispositivo ha bisogno di tensione per -> 2 ingressi => segnale in uscita dal comparatore

- Un integrato AND solo se i 2 ingressi sono alti avremo un'uscita altra serve a creare il leadtime > segnale impulsivo in impreso L> viene ritardata l'accensione del transistor -> non lo spegnimento (DEAD-TIME)

- OPTOISOLATORE -> permette di differenziare i ground mensa a) del sistema di controllo e quello di potenza prima di porre l'uscita dell'AND (Se avessimo lo stesso ground per tutti e dea in ingreso poniamo una resistenza per mail 25 passare , la i sistemi tutto sarebbe cortocircuitato). tensione in ingresso

- NOT -> nega il segnale impulsivo in ingresso per generare l' segnale di pilotaggio del secondo transistor, comple mentare al primo

- Struttura del HALF - BRIDGE

Il segnale impulsivo è il segnale di riferimento (onda quadra) dal filtro RC invece viene fuori un'onda che rapresenta la carica e la scarica del condensatore del filtra. Dal confronto (che avviene nel comparatore) tra il segnale di riferèmento e il segnale in uscita dal filtro RC viene fuori un'onda quadra (stesso andamento del segnale di riferimento in ingresso), una sfasata rispetto al riferimento di un intervallo di tempo pari al DEAD-TIME. Così, tramite l'utilizzo di un ponte RC, abbiamo implementato i la DEAD-TIME. L'aptoisolatore è formato da un fatodiado che, sottoposto a tensio mi troppo elevate, si romperebbe ecco perché viene usata la resistenza che limiti la tensione in ingresso all'optoisolatore È importante sempre leggere il DATASHEET degli strumenti prima di usarli. comprensivi Dall'AND viene fuori il segnale di pilotaggio di deadtime applicato all'accensione. Usiamo due AND perché abbiamo bisogno di un segnale per pilotare il transistor superiore (in ingresso all'AND avremo l'uscita dal comparatore e l'ingresso impulsivo data dal generatore iniziale), e di un segnale per pilotare il transistor Inferiore (in ingresso all'AND avremo l'uscita dal comparatore e Il segnale impulsivo negato così da creare la complementarietà dei transistor) del pilotaggio Il terminale centrale dell'optoisolatore viene collegato al gate dei transistor perciò inseriamo delle resistenze (resistenze di gate) per limitare la corrente che viene inserita nel gate. Correnti di picco troppo elevate deteriorare il gate man mano che si verifica no gli switch. Tra la resistenza e l'induttanza del carico inseriamo una sonda di corrente per poter misurare, tramite pl'oscilloscopio, la corrente sul carico. Sonda di corrente = amperometro. Simulazione INTERACTIVE -> in tempo realeМамочества

Dimensionamento del Dead Time

Il Dead time di solito è dell'ordine di grandezza dei ed è più grande per i BIT piuttosto che per i Mosfet ( microsecond. per i BIT) Per dimensionare il dead Time si guarda la scheda tecnica del dispositivo, ed in particolare i tempi di accensione e spegnimento dei transistor, così da poter misurare il valore di custo intervallo di tempo, in cui la corrente va a zero per definire il dead time stem Il Dead time garantisce lo spegnimento del transistor superiore prima dell'accensione dell'altro (à dispositivi non possono mai essere accesi contemporaneamente perché si avrebbe cortocircuito), ma crea delle deformazioni nella corrente sul carico che sarà inferiore rispetto a quella che è calcolata non considerando il dead time. Dal ponte RC viene fuori il segnale filtrato. L'andamento sarà quello tipico di un segnale del circuito RC con carica e scarica del condensatore. (Ricorda il segnale in ingresso al ponte è quello dato dal generatore di segnale). La costante di tempo del circuito deve essere molto più PICCOLA del periodo del segnale di pilotaggio. Il comparatore confronta il segnale filtrato in uscita dal ponte RC con un segnale di riferimento (Vzf). Quando il segnale filtratopsarà (sp) MAGGIORE della Vref avremo segnale in uscita dal comparatore alto, se MINORE sarà basso Sf > Vref => segnale d'uscita del comparatore sf < Vref => " ALTO BASSO Per avere dead time basi viene utilizzata una Viel piccola così che il segnale d'ingreso (Sf) sia più alto di Viel per pi intervali di tempo ampi (il dead time viene considerato solo quando Vy maggiore di g).Il segnale in uscita dal comparatore va in ingresso all'AND. con l'AND vengono confrontati il segnale d'uscita del comparatore è il segnale dato dal generatore iniziale. Quando entrambi i segnali sono alti (solo in questo caso) viene ritardata l'accen sione del transistor (NON lo SPEGNIMENTO) definendo così il Lead time. Il segnale d'uscita dall'AND va in ingresso all'OPTOISOLATORE che serve a controllare la potenza Le possiede , due ground indipendenti. Il NOT serve a negare il segnale di ingreso definito dal generatore per implementare il pilotaggio COMPLEMENTARE del secondo transi stor rispetto al primo Per calcolare il dead time su MULTISIM prendiamo l'oscillo Scopio dlove vengono disegnati i due segnali di pilotaggio dopo aver implementato il dead time) e calcolare, spostando l'istante le due barre di trigger, Ela differenza tra il valore in cui IL primo impulso scende e quello in cui il secondo impulso ( quello del transistor in basso) sale. Questa differenza sarò proprio il dead time. Poi andiamo a calcolare l'errore sulla tensione d'uscita AV. e la riduzione che abbiamo avuto su essa rispetto al valore dela tensione atteso Và (valor medio)

ANALISI DI FOURIER

Analisi Armonica del segnale di Ground

De component: tensione d'uscita dato dal simulatore THD : indice di distorsione armonica -> somma dei quadrati ( percentuale) delle armoniche (eccetto la fondamentale) divisa per la fondamentale La 3° armonica dovrebbe essere di ampiezza pari ad 1 di quela della 1°, invece dal simulatore la sua ampiezza éulteriormente ridotta. Queste armoniche a basse frequenza sono di piccola ampiezza ma sono difficili da filtrare.

Analisi armonica sulla corrente

L'unica considerazione da fare è sul THD

PROVA CON Vreg=2V

Differenza nel dead time calcolato rispetto alla prova con 3V Dead Time più piccolo. (Si usano, per sistemi più complessi tensioni di riferimento più basse per avere dovol time piccoli) le impostazioni dello spettro armonico É possibile variare le variabili cliccando su V(17) o V(gnd_15VDC1). Possiamo variare il Mini delle grandezze sul sugli assi L'ultima casa da fare per l'analisi è l'errore tra le due prove

CALCOLO ERRORE:

AVd.30 - AVd_zu VDC_comp-2v - VDC_comp-3V

HALF BRIDGE DC/AC

Stesso schema circuitale dell'half bridge in configurazione DC/DC, ma il segnale modulante è SINUSOIDALE anziché costante. In più il carico non è collegato come nel DC/DC, ma è collegato al punto centrale dell'alimentazione (O) è il punto centrale dell'half bridge (A) VAO = tensione sul carico VAO = Via se conduce il transistor QA+ VAO= - Voc se conduce il trans QA-